## **CML Semiconductor Products**

PRODUCT INFORMATION

# FX203 Selcall Tone Codec with Microprocessor Interface

Publication D/203/3 November 1998 Provisional Issue

#### Features/Applications

- Single-Chip Selcall Codec

- CCIR, EEA or ZVEI/SZVEI Versions

- On-Chip General Purpose Timer Separate General Purpose 4-bit Input/2-bit Output Port

- Mobile or Handheld Selcall

- 4-bit Microprocessor I/O Data Port

- Powersave Facility

- Uses Low-Cost 4MHz Xtal

- Low-Power 5V CMOS Process

**FX203**

## Brief Description

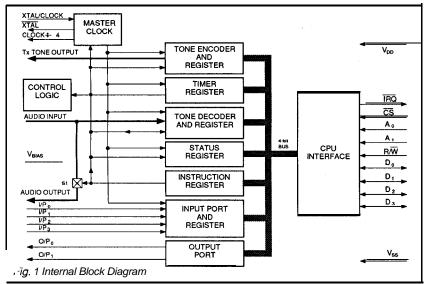

The FX203 is a single-chip 'N' tone Selective Call encoder-decoder peripheral intended for use with a host microprocessor. The device is available in 3 toneset formats, CCIR, EEA or ZVEI/SZVEI.

A 4-bit data I/O bus, 2-bit address,  $\overline{CS}$ , R/W and  $\overline{IRQ}$  lines are provided for connection to the microprocessor.

Separate general purpose 4-bit input and 2-bit output ports are available to allow external circuitry access to the microprocessor via this device. Functions such as 'PTT,' 'Rx Squelch,' 'Alert Bleeps' and 'Lamp Drivers' could operate through this facility.

An on-chip general purpose timer is provided

for such functions as Rx and Tx tone period timing. Time periods of between 1 Oms and 140ms in 1 Oms steps may be programmed via the microprocessor interface.

The FX203 reference oscillator utilizes a low-cost 4.0 MHz Xtal or externally derived clock. The divide by 4 (1 .O MHz) output may be used to drive the clock circuitry of other devices such as the FX365 CTCSS Encoder/Decoder, FX004 Voice Band Inverter, or the FX214 VSB Audio Scrambler.

The FX203 requires a single 5-volt supply and utilizes 'chip enable'/powersave' facilities for reduced current consumption in the Standby mode.

| Pin Number           |                            |  |  |  |  |  |  |

|----------------------|----------------------------|--|--|--|--|--|--|

| DIL<br>FX203*J       | Quad<br>FX203*L<br>FX203*I |  |  |  |  |  |  |

| 1                    | 1                          |  |  |  |  |  |  |

| 2                    | 2                          |  |  |  |  |  |  |

| 3                    | 3                          |  |  |  |  |  |  |

| 4                    | 4                          |  |  |  |  |  |  |

| 5                    | 5                          |  |  |  |  |  |  |

| 6                    | 6                          |  |  |  |  |  |  |

| 7                    | 7                          |  |  |  |  |  |  |

| 8                    | 8                          |  |  |  |  |  |  |

| 9                    | 9                          |  |  |  |  |  |  |

| 10<br>11             | 10<br>11                   |  |  |  |  |  |  |

| 12<br>13<br>14<br>15 | 12<br>13<br>14<br>15       |  |  |  |  |  |  |

| 16                   | 16                         |  |  |  |  |  |  |

| 17                   | 17                         |  |  |  |  |  |  |

| 18                   | 18                         |  |  |  |  |  |  |

| 19<br>20             | 19<br>20                   |  |  |  |  |  |  |

21

22

23

24

21

22

23

24

## **Function**

$A_o$ :

.s

\* C. E, Z tonesets

V<sub>pp</sub>: Positive supply rail. A single +5-volt power supply is required.

Audio Output: The received audio output, selected by the Audio Output Enable bit.

D, in the Instruction Register. This output could be the result of a squelch function. Audio Input: The audio input to the Tone Decoder and audio output switching. The composite (voice and tone) received audio requires to be coupled to this pin via

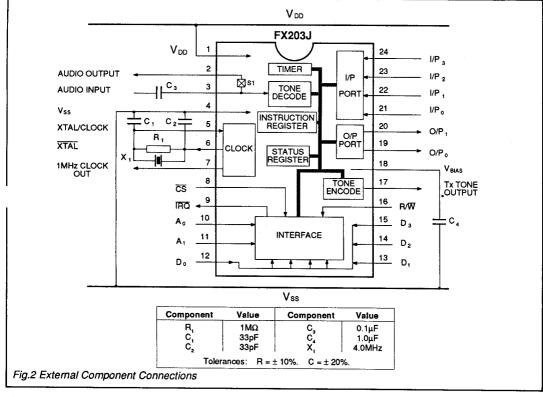

capacitor C<sub>3</sub>. See Figures 1 and 2.

V<sub>ss</sub>: Negative supply rail (GND).

Xtal/Clock: The input to the clock oscillator inverter. A 4.0 MHz Xtal or externally

derived clock should be connected here. See Figure 2.

Xtal: The output of the 4.0 MHz clock oscillator. See Figure 2.

Clock + 4: A 1.0 MHz (X, + 4) clock is available at this output for external use. Note

the output impedance and source current limits.

CS: The chip select input. A logic '0' on this pin will select the FX203. See Figure 3, Timing diagram.

IRQ: The Interrupt logic output. An active interrupt is set as a logic '0'. This pin can be wire OR'd to external circuitry. An external pullup resistor may be required on this

Conditions that cause Interrupt Requests are:

(1) Rx Ready (tone decoded) IRQ and Status bit Do (2) Timer Cycle expired IRQ and Status bit D,

(3) Input Port data change IRQ and Status bit D

register to be addressed via the CPU Interface (D<sub>0</sub> - D<sub>3</sub>) using the logic

states as detailed below. Register information is detailed on pages 4 and 5. R/W Register 0 0 O, Tone Encode Write 0 0 Instruction 1 0 1 0 Timer

Register address pins. These inputs, with the R/W input, select the internal

0 0 Tone Decode Read 1 Status Input Port

The 4-bit microprocessor interface for communication with the internal registers as directed by the An, A, and R/W inputs.

$\overline{R/W}$ : The Read/Write logic input, which with the  $A_n$  and  $A_1$  address inputs determine the Microprocessor/ Register communication. Read = logic'1', Write = logic '0'.

Tx Tone Output: The transmitted tone output of the Tone Encoder. Tone 'F' (Notone) will cause this output to go to  $V_{\text{\tiny RIAS}}$  . When not enabled this output is high impedance.

$m V_{BIAS}$ : The output of the on-chip bias circuitry, held at  $\rm V_{DD}/2$ . When the Encoder is not enabled this pin will be at  $\rm V_{SS}$ . This pin requires to be decoupled to  $\rm V_{SS}$  with a capacitor, C,.

O/P<sub>n</sub>: The 2-bit logic output port whose state is controlled by the Instruction  $O/P_1$ : Register  $(D_2, D_3)$ .

I/P<sub>1</sub>: I/P<sub>2</sub>: I/P<sub>3</sub>: The 4-bit logic input port. See page 5. These pins each have an internal  $1M\Omega$  pullup resistor.

## **External Components**

## **General and Operational Notes**

#### **Power-up Arrangements**

It is recommended that the following sequence be employed to set all internal registers to a start-up state upon power-up.

Write – Hex. '0' to Timer Register for a period greater than Power-Up Reset Time (TS).

The following actions clear the Status Register and reset all interrupts.

Read - Status Register.

Read - Tone Decode Register.

Read - Input Port Register.

Write – To Output Port as required.

The data in the Decoder Register is not valid until after the first active Decoder interrupt has been received.

#### Operation

Operation of the FX203 is Full Duplex.

The receive mode is achieved by writing any Timer setting except Hex. '0.'

The Tone Decode Register must be read before the expected arrival of the next tone, as register contents are overwritten.

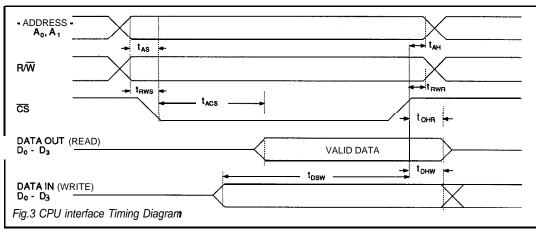

Data written to the device via the CPU Interface is acted upon at the end of the Data Set-up Time ( $t_{DSW}$ ), when the  $\overline{CS}$  input goes high (logic '1').

The Timer may be written to at any time. The Timer is reset when data is written to it. The new Timer period starts when the  $\overline{\text{CS}}$  input goes high (logic '1').

#### Layout

All external components (as recommended in Figure 2) should be kept close to the package.

Tracks should be kept short, particularly the Audio and  $V_{\text{BIAS}}$  inputs.

Xtal/clock and digital tracks should be kept well away from analogue circuitry. Analogue inputs and outputs should be screened wherever possible and the high level Tx Tone Output kept separate from other analogue inputs and outputs.

A "ground plane" connected to  $V_{ss}$  will assist in eliminating external pick-up.

## **Internal Register States**

The following descriptions show the condition of each of the 6 registers used by the FX203 to communicate with both microprocessor and radio systems. Table 1 details the hexadecimal 4-bit data words used in these registers. Timing information for the CPU Interface is given in Figure 3.

| Instruction Register |        | Wr                                                                      | Only $R/\overline{W} = 0 A_1 = 0 A_0 = 1$ |                                               |  |  |  |

|----------------------|--------|-------------------------------------------------------------------------|-------------------------------------------|-----------------------------------------------|--|--|--|

| Bit No               | Logic  | The Instruction Register addresses the functions of the FX203  Function |                                           |                                               |  |  |  |

| $D_{o}$              | 1      | Tx Enable :                                                             | _                                         | Enables the Transmitter circuitry.            |  |  |  |

| -                    | 0      |                                                                         | _                                         | Disables the Transmitter circuitry.           |  |  |  |

| D,                   | 1      | Audio Output Enable :                                                   | _                                         | Switches the Audio Input to the Audio Output. |  |  |  |

|                      | 0      |                                                                         | _                                         | Disables the Audio Output switch (S1).        |  |  |  |

| $D_2$                | 1 or 0 | Output Port O/P <sub>o</sub> :                                          | _                                         | The logic state of this line.                 |  |  |  |

| $\overline{D_3}$     | 1 or 0 | Output Port O/P, :                                                      | _                                         | The logic state of this line.                 |  |  |  |

| Tone Encode Register |                | Write | Onl            | у              | $R/\overline{W} = 0 A_1 = 0 A_0 = 0$ |

|----------------------|----------------|-------|----------------|----------------|--------------------------------------|

|                      | D <sub>o</sub> | D,    | D <sub>2</sub> | D <sub>3</sub> |                                      |

|                      | LSB            |       |                | MSB            |                                      |

| Tone Decode Register |                | Read | l Oni          | у              | $R/\overline{W} = 1 A_1 = 0 A_0 = 0$ |

|----------------------|----------------|------|----------------|----------------|--------------------------------------|

|                      | D <sub>o</sub> | D,   | D <sub>2</sub> | D <sub>3</sub> | 1906                                 |

|                      | 100            |      |                | MCD            |                                      |

The 4-bit Hex. word in this register will indicate the frequency (Table 1) of the received tone

| Timer Register           |                    |                | Write   | Only           | y              |              | $R/\overline{W} = 0 A_1 = 1 A_0 =$ |        |       |

|--------------------------|--------------------|----------------|---------|----------------|----------------|--------------|------------------------------------|--------|-------|

|                          |                    | D <sub>o</sub> | D,      | D <sub>2</sub> | D <sub>3</sub> |              | 7/4.0                              |        |       |

|                          |                    | LSB            |         |                | MSB            |              |                                    |        |       |

| The 4-bit Hex. word writ | tten to this regis |                | utomat  | tically i      |                | timer and s  | tart a timing c                    | cle as | shown |

|                          | Hex Code           |                |         |                |                | tion/Tone P  |                                    |        |       |

|                          | 0                  |                | _       | Disab          | le Recei       | ver. Transmi | tter and Time                      | r      |       |

|                          | Re                 | set and s      | tart to |                |                |              |                                    | •      |       |

|                          | 1                  |                | _       | •              |                | 10ms         |                                    | Ì      |       |

|                          | 2                  |                | _       |                |                | 20ms         |                                    |        |       |

|                          | 3                  |                | -       |                |                | 30ms         |                                    |        |       |

|                          | 4                  |                | _       |                |                | 40ms         |                                    |        |       |

|                          | 5                  |                | -       |                |                | 50ms         |                                    |        |       |

|                          | 6                  |                | _       |                |                | 60ms         |                                    |        |       |

|                          | 7                  |                |         |                |                | 70ms         |                                    |        |       |

|                          | 8                  |                | _       |                |                | 80ms         |                                    |        |       |

|                          | 9                  |                | -       |                |                | 90ms         |                                    | İ      |       |

|                          | A                  |                | _       |                |                | 100ms        |                                    |        |       |

|                          | В                  |                | -       |                |                | 110ms        |                                    |        |       |

|                          | C                  |                | -       |                |                | 120ms        |                                    |        |       |

|                          | D                  |                | _       |                |                | 130ms        |                                    |        |       |

|                          | E                  |                |         |                |                | 140ms        |                                    |        |       |

Disable Timer operation only

## **Internal Register States**

| Status Register |                                                                                                                | Read Only                                                                                                                                                                              | $R/\overline{W} = 1 A_1 = 0 A_0 = 1$                      |  |  |  |  |  |  |

|-----------------|----------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|--|--|--|--|--|--|

|                 | The Status Reg                                                                                                 | gister indicates the source of any interrup                                                                                                                                            | ot                                                        |  |  |  |  |  |  |

| Bit No          | Condition                                                                                                      | A logic '1' in the Status Register indicates that the bit is Set The Interrupt line (IRQ) is a logic '0' when active                                                                   |                                                           |  |  |  |  |  |  |

| D <sub>o</sub>  | latched the 4-bi                                                                                               | rupt are <b>Set</b> when the Tone Decoder has it Hex. word into the Tone Decode Regis next tone is decoded or that information rupt are <b>Cleared</b> by reading the Status Register. | ster. This register requires to be a will be overwritten. |  |  |  |  |  |  |

| D,              |                                                                                                                | rupt are <b>Set</b> when the intervals programs<br>the interrupt are <b>Cleared</b> after reading                                                                                      |                                                           |  |  |  |  |  |  |

| $D_2$           | Input Port (I/P <sub>0</sub><br>D <sub>2</sub> and an inter<br>D <sub>2</sub> and the inte<br>Input Port regis | rupt are <b>Set</b> when the data state at the rrupt are <b>Cleared</b> by reading the Status                                                                                          | Input Port changes.<br>Register followed by reading the   |  |  |  |  |  |  |

| $D_3$           | This bit is unall                                                                                              | ocated. Set at a logic '0.'                                                                                                                                                            |                                                           |  |  |  |  |  |  |

| Input Port                                                                        |                | Read           | l Onl          | y              | $R/\overline{W} = 1 A_1 = 1 A_0 = 0$ |

|-----------------------------------------------------------------------------------|----------------|----------------|----------------|----------------|--------------------------------------|

|                                                                                   | D <sub>o</sub> | D <sub>1</sub> | D <sub>2</sub> | D <sub>3</sub> |                                      |

|                                                                                   | LSB            |                |                | MSB            |                                      |

| By reading this register the microproc<br>facility allows external systems to cor |                |                |                |                |                                      |

The FX203 caters for CCIR, EEA and ZVEI/Suppressed ZVEI sequential tone system frequencies in three tone sets, "C," "E" and "Z" respectively, as shown in Table 1.

See the 'Specifications' pages for overall FX203 Tone performance characteristics.

| Hex.<br>nput/Output | D <sub>3</sub> | D <sub>2</sub> | D, | D <sub>o</sub> | 'C' Tone Set<br>f <sub>o</sub> (Hz) | 'E' Tone Set<br>f <sub>o</sub> (Hz) | 'Z' Tone Set<br>f <sub>q</sub> (Hz) |

|---------------------|----------------|----------------|----|----------------|-------------------------------------|-------------------------------------|-------------------------------------|

| 0                   | 0              | 0              | 0  | 0              | 1981                                | 1981                                | 2400                                |

| 1                   | Õ              | Ö              | Ö  | 1              | 1124                                | 1124                                | 1060                                |

| 2                   | ŏ              | Ö              | 1  | ò              | 1197                                | 1197                                | 1160                                |

| 3                   | Ŏ              | ō              | 1  | 1              | 1275                                | 1275                                | 1270                                |

| 4                   | 0              | 1              | 0  | 0              | 1358                                | 1358                                | 1400                                |

| 5                   | 0              | 1              | 0  | 1              | 1446                                | 1446                                | 1530                                |

| 6                   | 0              | 1              | 1  | 0              | 1540                                | 1540                                | 1670                                |

| 7                   | 0              | 1              | 1  | 1              | 1640                                | 1640                                | 1830                                |

| 8                   | 1              | 0              | 0  | 0              | 1747                                | 1747                                | 2000                                |

| 9                   | 1              | 0              | 0  | 1              | 1860                                | 1860                                | 2200                                |

| Α                   | 1              | 0              | 1  | 0              | 2400                                | 1055                                | 2800                                |

| В                   | 1              | 0              | 1  | 1              | 930                                 | 930                                 | 810                                 |

| С                   | 1              | 1              | 0  | 0              | 2247                                | 2247                                | 970                                 |

| D                   | 1              | 1              | 0  | 1              | 991                                 | 991                                 | 885                                 |

| E                   | 1              | 1              | 1  | 0              | 2110                                | 2110                                | 2600                                |

| F                   | 1              | 1              | 1  | 1              | Notone                              | Notone                              | Notone                              |

## Specification

#### **Absolute Maximum Ratings**

Exceeding the maximum rating can result in device damage. Operation of the device outside the operating limits is not implied.

Supply voltage -0.3 to 7.0V

Input voltage at any pin (ref  $V_{ss} = OV$ ) -0.3 to  $(V_{DD} + 0.3V)$

Sink/source current (supply pins) +/- 30mA (other pins) +/- 20mA

Total device dissipation @T<sub>AMB</sub> 25°C 800mW Max.

Derating 10mW/°C

Operating temperature range: **FX203J** -30°C to +85°C (ceramic) -30°C to +70°C (plastic)

#### **Operating Limits**

All device characteristics are measured under the following conditions unless otherwise specified:

$V_{00} = 5.0V$ ,  $T_{AMB} = 25$ °C. Xtal/Clock  $f_0 = 4.0$  MHz. Audio level 0dB ref: = 775mV rms.

| Characteristics                                                                                                                                                                                                                                                                                                                                                                  | See Note                 | Min.                                 | Typ.                                                             | Max.                                  | Unit                                         |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------|------------------------------------------------------------------|---------------------------------------|----------------------------------------------|

| Static Values Supply Voltage Supply Current – Rx on, Tx and Timer Disabled Rx on, Tx Enabled, Timer Running                                                                                                                                                                                                                                                                      | 1                        | 4.5                                  | 5.0<br>1.25<br>3.0                                               | 5.5                                   | V<br>mA<br>mA                                |

| Interface Levels CPU Data Port (D <sub>0</sub> – D <sub>3</sub> ) In/Out Logic '1' Logic '0 Output Logic '1' Source Current Output Logic '0' Sink Current Three State Output Leakage Current Input Port (I/P <sub>0</sub> – I/P <sub>3</sub> ) & (R/W, A,,, A <sub>1</sub> , CS) Logic '1' Logic '0 Output Port (O/P <sub>0</sub> – O/P <sub>1</sub> ), (IRQ) Logic '1' Logic '0 | 8<br>9<br>10<br><b>2</b> | 3.5<br>-<br>3.5<br>-<br>4.0<br>-     |                                                                  | 1.5<br>120<br>360<br>4.0<br>1.5       | ν<br>μΑ<br>μΑ<br>μΑ<br>ν<br>ν<br>ν           |

| Impedances Input Port output Port Audio Input Audio Switch S1 'ON' Audio Switch S1 'OFF' Tx Tone Output (Enabled) Tx Tone Output (Disabled) Clock + 4 Output IRQ Output (Logic '1') IRQ Output (Logic '0')                                                                                                                                                                       | 11<br>11<br>11<br>14     | 0.1<br><br>0.1<br><br>1.0<br><br>1.0 | 1.0<br>15.0<br>1.0<br>2.0<br>10.0<br>1.0<br>3.0<br>25.0<br>150.0 | 50.0<br>5.0<br>10.0<br>100.0<br>500.0 | MΩ<br>kΩ<br>MΩ<br>kΩ<br>MΩ<br>kΩ<br>MΩ<br>kΩ |

| Encoder Tone Output Level Tone Frequency Accuracy 'C Tone Frequency Accuracy 'E Tone Frequency Accuracy 'Z Tone Output Risetime Total Harmonic Distortion                                                                                                                                                                                                                        | 1                        | -1.0<br>-4.0<br>-0.3<br>-0.3         | 0<br>fo<br>fo<br>fo<br>2.0                                       | +1.0<br>+4.0<br>+0.3<br>+0.3          | dB<br>Hz<br>%<br>ms<br>ms                    |

| Characteristics                                                                                                                                                                                                               |                                                                                  | See Note                       | Min.                                        | Тур.              | Max.                 | Unit                                         |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------|---------------------------------------------|-------------------|----------------------|----------------------------------------------|

| Decoder Signal Input Range Decode Bandwidth -                                                                                                                                                                                 |                                                                                  | 4                              | -26.0                                       | _                 | +7.0                 | dB                                           |

| Probability > 0.995 'C' Probability > 0.995 'E' Probability > 0.995 'Z                                                                                                                                                        |                                                                                  | 5<br>5<br>5                    | ±1.0<br>±1.0<br>±2.0                        | <del>-</del>      |                      | %<br>%<br>%                                  |

| Not Decode Bandwidth – Probability < 0.03 'C Probability < 0.03 'E Probability < 0.03 'Z' Noise Response Rate 'C' Noise Response Rate 'E Noise Response Rate 'Z Decode Response Time                                          |                                                                                  | 6<br>6<br>7,12<br>7,12<br>7,13 | -<br>-<br>-<br>-                            | 1.0<br>1.0<br>1.0 | ±3.0<br>±3.0<br>±4.5 | %<br>%<br>Digits<br>Digits<br>Digits         |

| Notone to Tone<br>Tone to Notone                                                                                                                                                                                              |                                                                                  | 5                              | 20<br>33                                    | 25                | ТР<br>58             | ms<br>ms                                     |

| Timing – (Figure 3) Address Set Up Time Read/Write Set Up lime Address Hold Time Read/Write Recovery Time Chip Select Access Time Output Hold Time (Read) Data Set Up Time (Write) Data Hold Time (Write) Power Up Reset Time | t <sub>AS</sub> trws t <sub>AH</sub> trwr trwr tacs OHR tosw t <sub>DHW</sub> TS |                                | 50<br>50<br>0<br>0<br>0<br>150<br>20<br>3.0 |                   | 250<br>100           | ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns<br>ns |

- Notes 1.

- No Tx Tone load. Sink/Source currents \$0.1 mA. 2.

- 3. To 90% of nominal output, (from 'F tone' to 'not-F tone').

- 4. Sine or Square, a.c. coupled input.

- 5.

- With minimum tone period (Tp) for the tone set, S/N ratio 0dB.

Under all conditions of input amplitude and S/N ratio, with maximum Tp specified for the tone set. 6. 7. Gaussian Noise Input 6kHz band limited with a maximum input level corresponding to I-digit code

- falsing rate. (random to random single characters). 6. With each data line loaded as: C = 50pf and  $R = 10k\Omega$ .

- 9.  $V_{OUT} = 4.6V$

- 10.

- $V_{\text{OUT}} = 0.4\text{V}$ External connections on the Audio Output may alter these values. 11.

- Single digit response in a 40.0-hour period. 12.

- 13. Single digit response in a 1 .O-hour period.

- An emiter follower output with an internal 10kΩ pulldown resistor. 14.

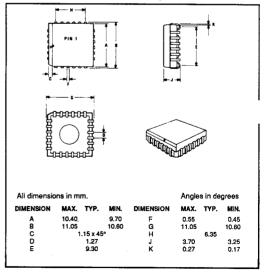

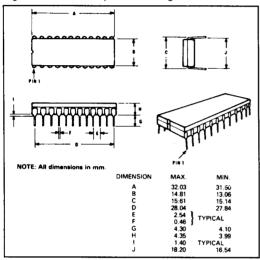

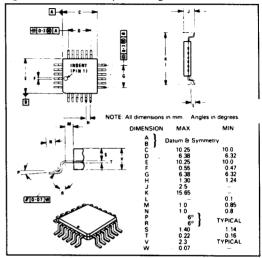

## **Package Outline**

The FX203J, the cerdip package is shown in Figure 4. The 'LG' version is shown in Figure 5 and the 'LS' version in Figure 6.

To allow complete identification, the 'LG' and 'LS' packages have an indent spot adjacent to pin 1 and a chamfered corner between pins 3 and 4. Pins number anti-clockwise when viewed from the top (indent side).

Fig. 4 FX203\*J 24-pin DIL Package

## **Ordering Information**

\* Insert the required system toneset

*CCIR EEA ZVEI/SZVEI* ' (C) (E) (Z)

**FX203(\*)J** - Figure 4

24-pin cerdip DIL

FX203(\*)LG - Figure 5

24-pin quad plastic

encapsulated bent and cropped

FX203(\*)LS - Figure 6

24-lead plastic leaded chip

carrier

## **Handling Precautions**

The FX203 is a CMOS LSI circuit which includes input protection. However precautions should be taken to prevent static discharges which may cause damage.

Fig. 5 FX203\*LG 24-pin Package

Fig. 6 FX203\*LS 24-pin Package